As you may or may not know, I'm currently working on a Papilio Wing that streams and receives multiple channels of audio over Ethernet using the 5 layer TCP/IP model. The wing includes as an ADC a PCM1807 with a companion PLL1705 to generate the sampling clock frequencies. As a DAC it uses a MAX5556 and as the ethernet controller the ENC28J60.

Here is a render of the PCB and the actual PCB

By the way... I manufactured my PCBs with Elecrow and I have to say I am impressed with their quality. They are really cheap and really good :D.

Anyway... I've just received my Papilio and I'll be posting stuff as I progress.

The first thing I did was to be shure that the PLL was working, so I made a little test module in VHDL that turned on and off a couple of LEDs synchronously with the PLL output clock. Here is the code. Note tha it uses an IP module from Xilinx called DCM. This module is like a programmable PLL and is the one that converts the input 32MHz clock to the 27MHz clock for the PLL1805. You can get more info here http://papilio.cc/index.php?n=Papilio.DigitalClockManager

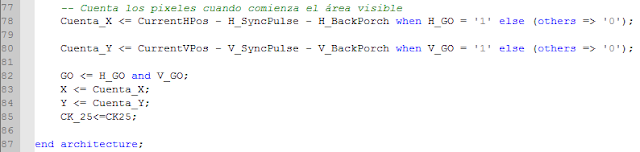

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Test_PLL is

port(

CK32 : in STD_LOGIC; -- Main Papilio Clock (32MHz)

CK27 : out STD_LOGIC; -- Clock from the Papilio to the PLL

CK384fs : in STD_LOGIC; -- Clock from the PLL to the Papilio

LED1 : out STD_LOGIC;

LED2 : out STD_LOGIC;

BTN1 : in STD_LOGIC;

BTN2 : in STD_LOGIC

);

end Test_PLL;

architecture Behavioral of Test_PLL is

COMPONENT DCM32to27

PORT(

CLKIN_IN : IN std_logic;

CLKFX_OUT : OUT std_logic;

CLKIN_IBUFG_OUT : OUT std_logic;

CLK0_OUT : OUT std_logic

);

END COMPONENT;

signal led1_signal : STD_LOGIC := '0';

signal led2_signal : STD_LOGIC := '1';

begin

Inst_DCM32to27: DCM32to27 PORT MAP(

CLKIN_IN => CK32,

CLKFX_OUT => CK27,

CLKIN_IBUFG_OUT => open,

CLK0_OUT => open

);

-- This process reacts to one of the output clocks of the PLL

blink: PROCESS(CK384fs)

variable counter : INTEGER := 0;

BEGIN

IF(rising_edge(CK384fs)) THEN

IF(BTN1 = '1' and BTN2 = '0') THEN -- Button 1 pressed

counter := counter + 1;

IF(counter >= 1700000) THEN

led1_signal <= not(led1_signal);

led2_signal <= not(led2_signal);

counter := 0;

END IF;

ELSIF(BTN1 = '0' and BTN2 = '1') THEN -- Button 2 pressed

counter := counter + 1;

IF(counter >= 17000000) THEN

led1_signal <= not(led1_signal);

led2_signal <= not(led2_signal);

counter := 0;

END IF;

END IF;

END IF;

END PROCESS;

LED1 <= led1_signal;

LED2 <= led2_signal;

end Behavioral;

You can also download the Xilinx project from my Github https://github.com/DiegoRosales/VHDL_Modules.git.