Como ustedes sabrán (o no), hace como 10 minutos aprendí que practicamente todos los FPGAs tienen unos módulos especiales para almacenar datos y leerlos. A estos módulos en inglés se les llama "Look Up Table" o LUT. Esto en cristiano significa algo así como "Ve a ver si ya puso la marrana", pero pues a pesar de que esto lo decimos con el fin de que se vayan a dejar de "molestar", ya que muy probablemente la marrana no ha puesto nada, en el mundo de los FPGAs, la marrana muy probablemente ya puso algo que necesitamos. El caso es que estos módulos almacenan datos y los podemos usar y ordenar como queramos. Un dato importante es que a este tipo de memoria, también se le llama RAM distribuida (Distributed RAM). Para el caso del Spartan 3E, que es el que usa el Basys2, esta memoria varía entre 15 y 38Kbytes, dependiendo cuánto quieras pagar.

Usar esta RAM es algo realmente fácil, y lo hacemos todo el tiempo cuando almacenamos constantes y cosas así, pero ahora la vamos a usar como se debe (más o menos). En estos ejemplos vamos a construir un bloquecito de RAM de 8x8 (8 registros de 8 bits). Este ejemplo es cuando queremos leer la RAM de manera asíncrona. Más adelánte postearé un tutorial de RAM con lectura síncrona

RAM Asíncrona

Primero comenzamos con la declaración de librerías y de puertos.

Necesitamos declarar ciertas constantes para que nuestro código se pueda adaptar fácilmente. Los puertos que necesitamos son la dirección de la memoria, el dato a enviar, una señal que nos indique cuándo podemos escribir y por último la lectura de la memoria en la dirección deseada.

Ahora nos vamos a la parte de la arquitectura. El truco aquí es crear una matriz de datos (8x8), por lo que necesitamos declarar un nuevo tipo. Llamémosle "tipo_ram". También hay que declarar una señal con este tipo

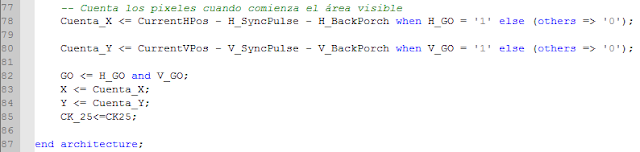

Por último hay que declarar la manera en la que se va escribir y accesar la memoria.

Nótese que la escritura es síncrona y está controlada por la entrada "escribir". Si esta entrada esta en '0', no escribe y nada más lee. Hay que realizar cambios de tipos, ya que la entrada "dir" esta en "std_logic_vector", pero el índice de la variable "ram" que es "tipo_ram" debe ser "integer".

Como pordán ver la simulación funciona de maravilla. El dato se escribe cuando tenemos un flanco positivo en el reloj y cuando "escribir" es '1'.

Este ejemplo lo saqué de un libro titulado "FPGA Prototyping by VHDL Examples - Xilinx Spartan 3 Version", aunque le modifiqué algunas cosas, como el tamaño de el bloque de la RAM.

Ahora les dejo el código .vhd y los archivos de la simulación

Código .vhd

Simulación usando ActiveHDL

My Github

https://github.com/DiegoRosales